信号面叠加的注意事项

你能学到的:

简单的pcb通常在2层板上工作得很好,但高级设计需要更加小心,以确保信号完整性和电源完整性。

对于高速板和高速/低电平板,平面层也需要正确放置,以保证电源完整性和信号完整性。

为电路板设计正确的层堆叠也有助于抑制信号网络之间的串扰,并且是控制PCB阻抗所必需的。

这种高密度板与高速组件将需要多层PCB堆叠。

PCB中的每一层都在决定电学行为方面起着特定的作用。信号平面层在组件之间传输电源和电信号,但除非在内层中放置正确的铜平面排列,否则它们可能无法正常工作。你的PCB需要电源层和接地层,除了信号层,你需要把这些放在你的PCB堆叠中,以确保你的新板正常工作。

那么哪里是放置电源、地面和信号层的最佳位置呢?这是PCB设计中长期争论的问题之一,迫使设计师仔细考虑他们的电路板的预期应用,组件如何工作,以及电路板中的信号公差。如果您了解阻抗变化、抖动、电压纹波vs. PDN阻抗和串扰抑制的限制,您可以确定在电路板中放置的信号和面层的正确安排。

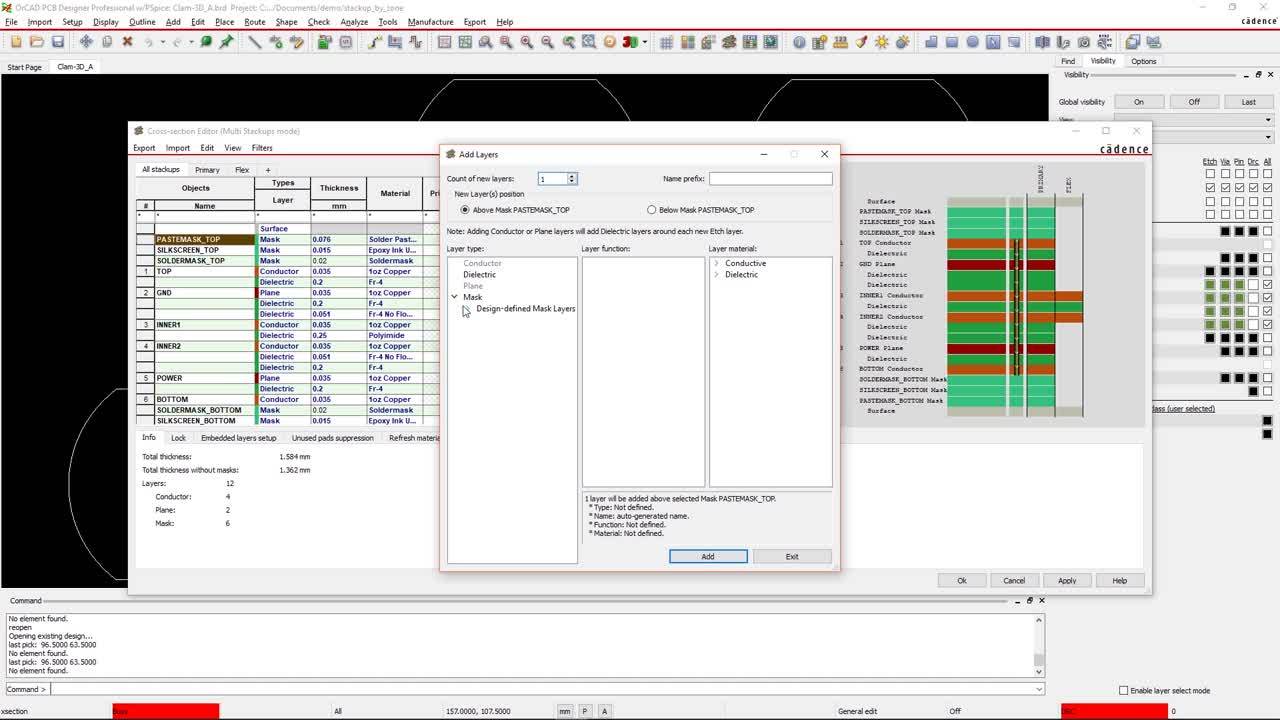

将您的设计意图变为现实需要一套正确的PCB设计工具。无论您是需要创建简单的两层板还是具有数十层的高速PCB,您的PCB设计软件都需要适应任何应用。下面是在创建PCB堆栈时需要考虑的一些重要事项。使用Allegro中的PCB设计功能,您可以将理想的层堆栈定义为板的模板,并且可以设计和分析PCB的各个方面。

PCB堆叠需要多少层?

当涉及到定义信号面叠加时,入门级设计师可能倾向于极端地思考。要么每块电路板只需要两层,要么每一小组痕迹都需要一个专用层。正确答案介于两者之间,这取决于电路板中的网数、电路中可接受的纹波/抖动水平、是否存在混合信号等等。

一般来说,如果你的概念证明在面包板上可以很好地工作,你可以在两层板上使用任何你喜欢的布局技术,你的板很可能会正常工作。最多,对于高速信号(见下文),您可能需要采用网格接地方法,以提供某种最低水平的EMI抑制。对于运行在高速或高频(或两者兼有)的更复杂的设备,您至少需要一个四层PCB堆叠,包括电源平面、接地平面和两个信号层。

该板上的信号平面堆叠只有两层,使其成为高速设计的糟糕选择。

在确定所需的信号平面层数时,首先要考虑的应该是信号网的数量以及信号之间的近似宽度和间距。当你试图估计你在堆栈中需要的信号层数时,你可以采取两个基本步骤:

确定净计数:原理图中的简单净计数和建议的电路板尺寸可用于估计电路板中需要的信号层数。层数一般与分数(净计数*迹宽)/(板宽)成正比。换句话说,更多的网和更宽的走线要求电路板更大或需要使用更多的信号层。在这里,您必须根据您的经验来确定对于给定的板尺寸,您需要保持所有网络的确切信号层数。

在你的平面层中添加:如果你需要控制信号层的阻抗路由,你现在需要为每个信号层放置一个参考层可控阻抗信号层.如果组件密集排列,则需要在组件层以下设置一个电源平面,因为表层没有空间放置电源轨道。这可能导致高净计数HDI板所需的表面层数达到两位数,但参考层将提供屏蔽和一致的特性阻抗。

一旦确定了多层板的正确层数,就可以继续在PCB堆栈中安排层数。

设计您的PCB层堆栈

PCB堆叠设计的下一步是安排每一层以提供跟踪路由路径。您的层堆栈通常围绕中心核心层对称布置,以防止在高温组装和操作期间翘曲。平面层和信号层的排列是关键可控阻抗路由,因为您需要为不同的轨迹安排使用特定的方程,以确保控制阻抗。

为刚性-挠性堆叠设计,您需要在堆栈中为刚性和柔性区域定义不同的区域。Allegro中的层堆栈设计工具使这个过程变得容易。在将原理图捕获为空白PCB布局后,可以定义层堆栈和不同层之间的过渡。然后,您可以继续确定受控阻抗路由所需的跟踪尺寸。

带状线与微带线和控制阻抗

对于受控阻抗,在两个平面层之间的内部层上路由的走线应该使用带线阻抗方程设计。这个方程定义了带状线具有特定特性阻抗值所需的几何形状。因为方程中有三个不同的几何参数来决定阻抗,所以最简单的方法是首先确定所需的层数,因为这将确定给定板厚度的层厚度。内部信号平面层的铜重量通常为0.5或1盎司/平方英尺。ft.这就剩下跟踪宽度作为要确定的最后一个参数对于特定的特性阻抗。

同样的程序适用于表面的微带痕迹。确定层厚度和铜重量后,只需确定需要用于定义的特性阻抗的迹线宽度。Allegro中的PCB设计工具包括一个阻抗计算器,可以帮助您调整走线的大小,以便定义特征阻抗。如果需要使用微分对,只需将每一层中的迹线定义为微分对,阻抗计算器将确定迹线之间的正确间距。

四层板特性阻抗计算器。

检查PCB布局中的阻抗

当你在真正的电路板上布线时,它们可以电容式或电感式耦合到其他线路和导体上。由附近导体产生的寄生电容和电感改变了实际布局中的迹阻抗。为了确保您在堆栈中的所有层都达到了阻抗目标,您需要一个阻抗分析工具来跟踪整个选定信号网络的阻抗。如果您可以看到PCB布局中标记的不可接受的大变化,您可以快速选择迹线并调整路由以消除互连中的这些阻抗变化。

如下图所示,沿轨迹的大阻抗变化用红色标记。应调整该区域的迹线之间的分离,以消除这种阻抗变化或使其在可接受的公差范围内。您可以在设计规则中定义所需的阻抗公差,布局后阻抗计算器工具将根据所需的阻抗值检查您的路由。

在Allegro中使用阻抗工作流分析仪确定沿两条轨迹的特征阻抗变化。

模拟vs.数字部分和你的图层堆叠

在上面的讨论中,我们只讨论了数字信号,因为它们的要求比模拟系统高得多。全模拟板和混合信号板呢?对于模拟板来说,电源完整性要容易得多,但信号完整性要困难得多。对于混合信号板,您需要将上面所示的数字方法与这里所示的模拟方法结合起来。

数字信号的带宽可以延伸到某个较高的频率,对于二进制信号,通常以膝盖频率作为频率。膝关节频率约为0.35/(上升时间),对于上升时间为1 ns的信号,膝关节频率为350 MHz。为了更快的数字信号降低到~ 20ps,膝盖频率现在扩展到17.5 GHz。对于模拟信号,带宽要窄得多,您只需要担心这个带宽内的电源平面阻抗和插入/返回损失。这使得电源完整性和信号完整性更容易;信号链或高PDN阻抗在此带宽之外的任何损失都可以忽略。

高层数PCB上集成电路的电磁仿真模型。

信号隔离

另一种选择是更先进的,需要使用接地铜浇注或通过围栏,以确保隔离之间的不同部分的板。如果你在模拟迹线旁边运行地倒,你就创建了一个共面波导,它具有高隔离性,是路由的常见选择高频模拟信号.如果您想使用通栅或其他高频导电隔离结构,您应该使用电磁场求解器来检查隔离,并确定是否应该选择在不同的信号层中进行隔离。

回程路径规划

在电路板上混合模拟和数字信号对跟踪位移电流的地面返回路径以及数字和模拟板部分之间的隔离提出了严格的要求。你的电路板应该这样布置,使模拟返回路径不会在数字元件附近交叉,反之亦然。这可以像将数字信号和模拟信号分离到由各自的地平面分隔的不同层一样简单。虽然这会增加成本,但它确保了不同部分之间的隔离。

如果您的模拟组件从交流电源供电,您的模拟组件可能还需要专用的模拟电源平面。这是电力电子以外的罕见情况,但只要你能分析,从概念上讲很容易处理回程路径规划.如果您将模拟电源部分置于上游并与数字电源部分分离,则可以将单个电源平面用于两种类型的信号。如果你正确地规划了返回路径,你就可以防止不同电源部分和接地部分之间的干扰。适用于直流电源部分切换监管机构,直流部分的开关噪声需要与交流部分隔离,就像数字信号需要与模拟信号隔离一样。

在Allegro中模拟返回路径。这表明,返回路径穿过地平面的间隙(绿色箭头所示),为该信号创建了一个大的环路电感,使其容易受到串扰。

你的堆叠是信号和功率完整性的主要决定因素,你需要这样的权利PCB设计和分析软件来创建一个PCB周围你想要的堆栈。设计工具Allegro PCB Designer从节奏集成全套分析工具用于检查信号和电源完整性的各个方面。本设计平台集成功能强大SI/PI分析点工具,为您提供验证下一个系统的信号和电源完整性所需的分析功能。此外,你可以在这里得到更多的设计技巧电子书.

如果您想了解更多Cadence如何为您提供解决方案,跟我们和我们的专家团队谈谈吧.